John Simons

@johnsel92The ghost in your machine || Field programming your gate arrays and coding PCBs in @JITXsoftware

Similar User

@tiantianjin2

@VE7LTN

@HRCrusader

@HardwareTeams

@F6GNJ

@TB2REV

@luzooki

@bablogy

@BrainWizard2

@aditya_bhandoh

@Sarka_VS

@HaraldBlab

@RigoLigoRLC

@frid_genius

@NagaApi7697

#JLCPCBEngineersDay Save up to $125! JLCPCB support every engineer's innovative dreams. bit.ly/3Mt2IMe

Sometimes you have a weird ble enabled device with unknown protocol that you want to read out on pc and this is one way to do it #scanner #hack #hacker #hamradio ... youtube.com/shorts/PPL0ja9… #boondock

Finally got @GOWIN_SEMI GW5AST fpga working with Gowin Analyzer Oscilloscope on linux It took me few days to fix issues on linux, but windows experience was quite smooth. However if tools were open source it would've been better. Now I can play with DDR3 and PCIe on #GOWIN

LitePCIe support for @latticesemi CertusPro-NX (Gen3 X4) and @GOWIN_SEMI GW5 (Gen2 X4) is coming along nicely! 🚀 We've got MMAP accesses up and running and will focus on MSI(X) and DMA support. All using the same Linux driver and LiteX integration as the other already…

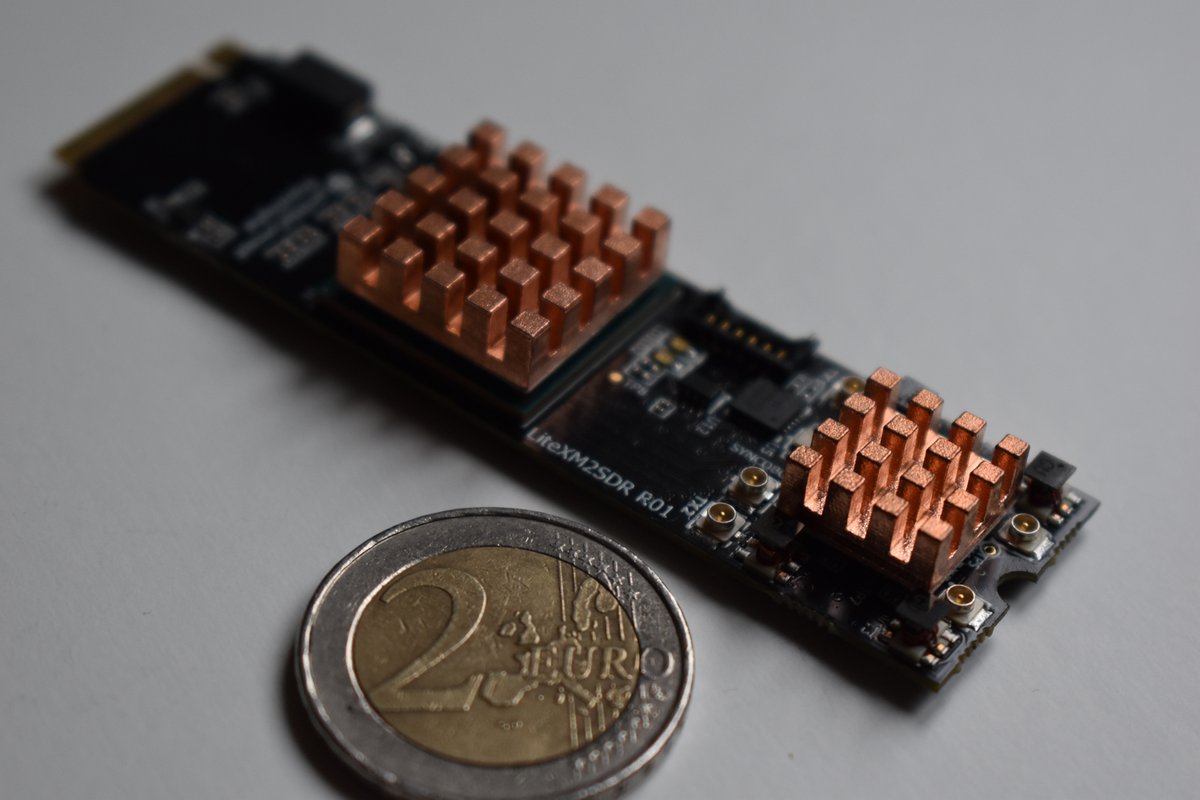

Beauty of (some) abstraction layers: Just tested the LiteX M2SDR as a Thunderbolt SDR ⚡️— no PCIe driver changes required and now fully plug & play! It just now need a proper 3D printed case for the SMAs/antennas 😅.

Releasing LiteX M2SDR initial gateware/software to start the conversation. Hardware arrives in a few weeks. Join us, share your thoughts, and let's innovate together! github.com/enjoy-digital/…

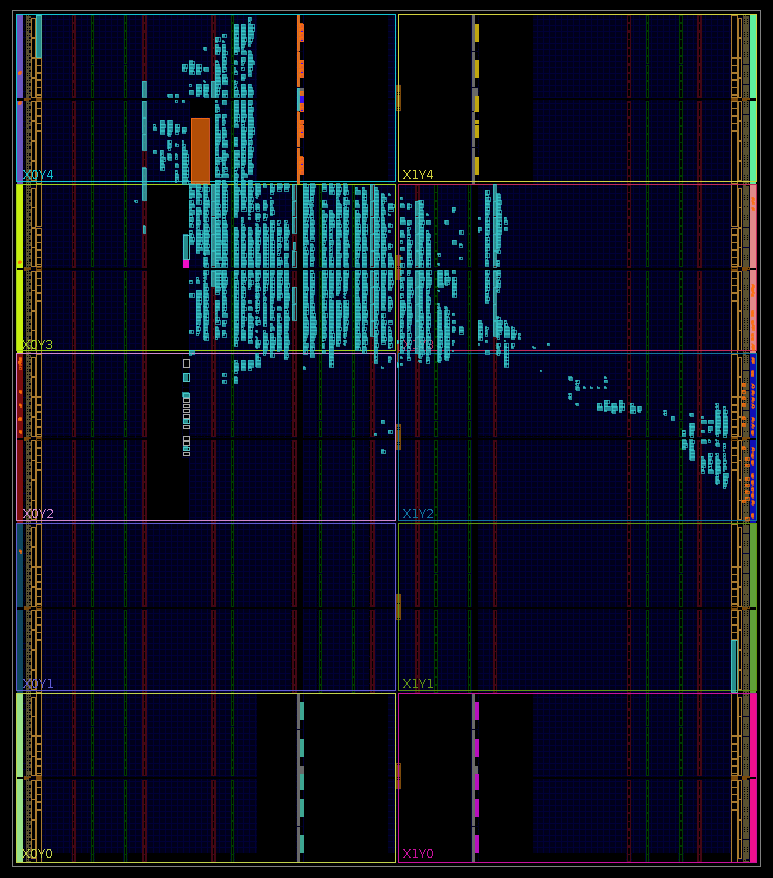

Current resource usage of the LiteX M2SDR FPGA (XC7A200T) with LitePCIe Gen2 X4: ~6% LUTs, %3% Regs, 12% BRAM, 0% DSPs -> Still plenty of space for custom RF processing :)

Very cool project by @enjoy_digital and @LambdaConcept

I think I finished implementing the line rendering in CyberEther using Signed Distance Fields to get rid of most aliasing. I'm happy with the results. I should merge Alpha 4 this weekend after running some tests on standard DPI displays. github.com/luigifcruz/Cyb…

Here is the Beta ThunderScope (open-source oscilloscope) with OCuLink! What host system should I start with? Intel x86, Raspberry Pi Compute Blade with A72, @element14_Avnet ZUBoard with A53, or @beagleboardorg BeagleV-Fire with RISC-V processor.

Adam Thompson and I will give a talk at the SciPy Conference this year in Tacoma, WA. We will talk about the new NVIDIA Holoscan DSP pipeline being developed for the Allen Telescope Array. And show real-time, high-bandwidth visualization in CyberEther. cfp.scipy.org/2024/talk/8AVL…

Spoke to @geoffreyhinton about OpenAI co-founder @ilyasut's intuition for scaling laws👇. "Ilya was always preaching that you just make it bigger and it'll work better. And I always thought that was a bit of a cop-out, that you're going to have to have new ideas too. It turns…

HectaScope ❤️ @nvidia The first signs of life of RDMA support for HectaScope, this means that your data will be copied from the HectaScope directly to your @nvidia GPU bypassing the CPU and RAM. This will allow real-time accelerated computing and machine learning on your 2GHz…

I just found out that there is such a thing as the tasselled wobbegong shark and I need to share it with you all

So .. let's run a really quick Xilinx IP quality check. Back in 2019, I commented about the quality of their AXI Ethernet Lite IP. You can read about this bug and others here: zipcpu.com/blog/2020/01/0…

It would be so great if we had a cheap PCIe device that people could use to learn how PCIe works, how to write drivers, etc.. without the need to build the hardware yourself as well. Think @Raspberry_Pi RP1 via M.2 or Thunderbolt.

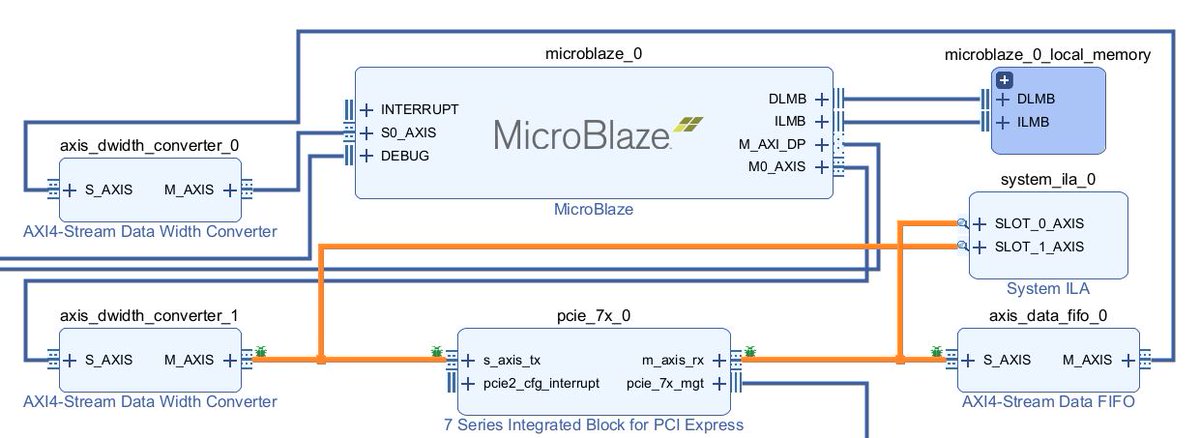

is there any way to learn how PCIe works for "devices" (since this is a Microblaze) I am seeing it coming up a low now that there's a new generator of domain-specific accelerators being built ...

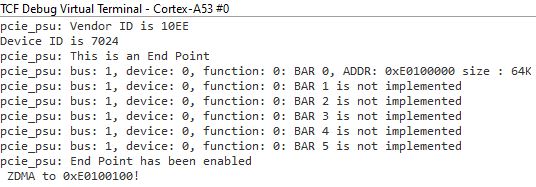

More progress on SW-defined TLP for PCIe! I got bare-metal PCIe and ZDMA working with ZUBoard to the Artix FPGA. This is an example of 128 Bytes in one packet. This is unique as root-driven DMA, whereas XDMA is endpoint-driven DMA.

United States Trends

- 1. ICBM 83,9 B posts

- 2. Dnipro 25,7 B posts

- 3. Good Thursday 19,7 B posts

- 4. #ThursdayMotivation 3.677 posts

- 5. Adani 609 B posts

- 6. Nikki Haley 26,3 B posts

- 7. Juice WRLD 21,7 B posts

- 8. #thisisme 37,3 B posts

- 9. #JinOnFallon 458 B posts

- 10. Happy Birthday Nerissa N/A

- 11. Bitcoin 591 B posts

- 12. #chillguy 50,2 B posts

- 13. #My82Playlist N/A

- 14. Ellen DeGeneres 63,8 B posts

- 15. Suns 11,4 B posts

- 16. Thomas Sowell 9.272 posts

- 17. Paul George 9.339 posts

- 18. Dunn 4.807 posts

- 19. SWARM 7.265 posts

- 20. Jasmine Crockett 37,2 B posts

Who to follow

-

tiantianjin

tiantianjin

@tiantianjin2 -

lorenzo baratta

lorenzo baratta

@VE7LTN -

@HamRadioCrusader

@HamRadioCrusader

@HRCrusader -

HardwareTeams.com

HardwareTeams.com

@HardwareTeams -

F6GNJ

F6GNJ

@F6GNJ -

Yusuf Coşgun

Yusuf Coşgun

@TB2REV -

PCBWay - Luz Woo

PCBWay - Luz Woo

@luzooki -

b a b a

b a b a

@bablogy -

Viet Van Dang | Grad Student

Viet Van Dang | Grad Student

@BrainWizard2 -

Aditya Bhandoh

Aditya Bhandoh

@aditya_bhandoh -

Sarka

Sarka

@Sarka_VS -

Harald Blab

Harald Blab

@HaraldBlab -

RigoLigo

RigoLigo

@RigoLigoRLC -

Young Ventura 🚀

Young Ventura 🚀

@frid_genius -

Naga Api

Naga Api

@NagaApi7697

Something went wrong.

Something went wrong.