STE

@hs_kuoSemiconductor technology enthusiast

Similar User

@dnystedt

@DrFrederickChen

@techfund1

@DylanOnChips

@ChipsandCheese9

@ChipsSaas

@_fabknowledge_

@witeken

@CDemerjian

@highyieldYT

@SKundojjala

@SemiconAlpha

@realmemes6

@dylan522p

@Wenyee_Lee

Great video from Chris Mack, the man who probably taught the most people in the world about lithography and modeling. He only got into it cuz his first day at the NSA, they had a litho tool being delivered and they didn't have anything for him to work on. youtu.be/k6z8RfvTxDg?si…

This is the example from ASML to see the world-wide cooperation for the most advanced scanner. If someone restrict components from solo supplier in supplier chain, then there will be no integration and no tool can be delivered.

The article “Keeping #MooresLaw on Track” from our friends and colleagues at @ASMLcompany highlights their latest efforts to bring #HighNA #EUV #lithography into production @IEEESpectrum bit.ly/44OqdXt #semiconductors

Part of U.S. #CHIPSAct funding is to address #metrology gaps in the #semiconductor ecosystem. @Fractilia CTO @ChrisMack describes the metrology capabilities needed for future chips in this @SemiEngineering article bit.ly/44KkJwA #NIST #eBeam #technology #manufacturing

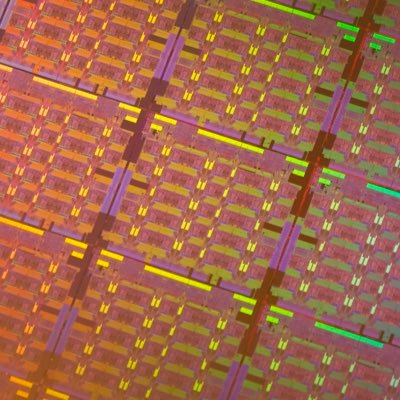

TSM Cross-node Chip Die Size Shrinks and Total Power Consumption Comparison. From TSM 2022 Sustainability Report lnkd.in/gPuteFrz

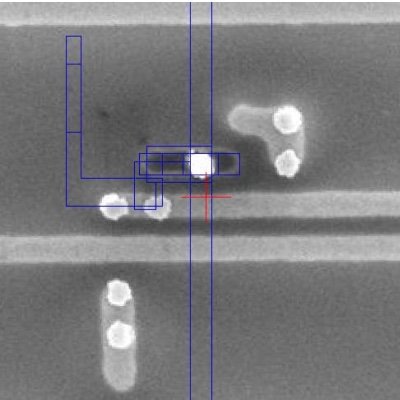

Overlay performance of Chip-on-Wafer bonding status and challenges from tsmc published in 2023 VLSI Symposium. It is interesting to see CSAM is implemented as bonding yield index. lnkd.in/gKPQynrR

New development for #EUV #stochastics control - #Fractilia #Overlay Package adds overlay #metrology to our solutions to further improve #EUV #patterning control and #yields bit.ly/3qDhqbI #lithography

Defect Density trend chart for 10/7/5nm of Qualcomm's products in Samsung Foundry. It looks good. From Qualcomm's paper in IEDM 2022 lnkd.in/gaib239H

Very interesting evolving graphs to show us how nano-TSVs connect backside PDN, ESD, latch-up, passive MIM capacitors or decoupled deep trench capacitors for full function 2-side SOC from imec ITF. It also paves the way for chiplet heterogeneous integrati…lnkd.in/gJYfpWNe

Interesting cost analysis for 2D SOC and 3DIC chiplet solution. 3DIC might lower the cost by 48%. From Xi-Wei Lin, Synopsys lnkd.in/gcta9Q3q

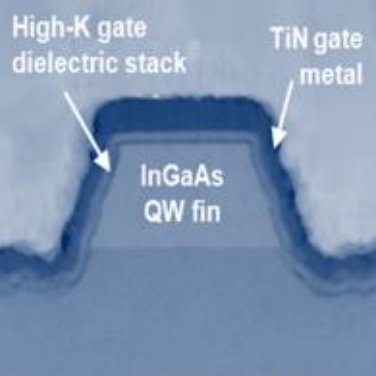

This could be another innovation to be watched out.

In this #SPIELitho recap article “Managing Yield with #EUV Lithography and #Stochastics” #Fractilia CTO Chris Mack presents on the importance of modeling #EdgePlacementError to #semiconductor #yield @SemiEngineering bit.ly/3MDycjn #Lithography

My opinions: 1. IFS is still in infant stage and need "Mother" to carry on. In IDM, usually designer is dominate and fab supports design for manufacturing. But in foundry, it "typically" does not proceed that way. 2. intel tested "selected customers" fou…lnkd.in/gC8kxXQu

"Apple will pay TSMC for known good die rather than standard wafer prices, at least for the first three to four quarters of the N3 ramp as yields climb to around 70%, Brett Simpson, senior analyst at Arete Research, said in a report provided to EE Times."…lnkd.in/gPyhhHr4

@Fractilia CTO Chris Mack describes the growing challenges facing CD SEMs for #5nm and below chip manufacturing in this new @SemiEngineering article bit.ly/3KQvc2g #semiconductor #stochastics #EUV #lithography #patterning

There are lots of published papers about SEM image "Denoising" using DL/ML/AI to improve image quality for pattern CD/roughness metrology or reduce frames to improve SEM productivity recently. For more than 2 years working on CD metrology, I fully agreed…lnkd.in/gmy4mrPe

Just curious about the cost added for BPR and found the paper published by imec in 2019 VLSI conference. The Ball Park estimation for these data: for BPR cost increase will be ~4%. The power track area saving could be ~10%. Total cost saving could be ~5%…lnkd.in/gsx9W2-Z

It is amazing to see the transmission XCD tool Axion T2000 debut from KLA, although I am a little bit late for this. Just wondering will it work well in logic process also? What are the lateral resolution and sensitivity for profile variation. Does it bec…lnkd.in/gBAYNK2E

United States Trends

- 1. #DWTS 28,2 B posts

- 2. #WWENXT 22,4 B posts

- 3. Carrie Ann 2.462 posts

- 4. Chandler 17,2 B posts

- 5. Stephen 51,1 B posts

- 6. Dame 51,5 B posts

- 7. Joey 19,6 B posts

- 8. Ilona 3.614 posts

- 9. Clemson 10,7 B posts

- 10. Sharon Stone 14 B posts

- 11. Rob Dillingham N/A

- 12. Rozier 1.907 posts

- 13. Effy 2.376 posts

- 14. Derek 16,7 B posts

- 15. Rudy 30,6 B posts

- 16. Herro 2.430 posts

- 17. #MAFS N/A

- 18. John Kerry 9.667 posts

- 19. Maliq Brown N/A

- 20. Ajax 7.061 posts

Who to follow

-

Dan Nystedt

Dan Nystedt

@dnystedt -

Fred Chen

Fred Chen

@DrFrederickChen -

Tech Fund

Tech Fund

@techfund1 -

Semiconductor News by Dylan Martin

Semiconductor News by Dylan Martin

@DylanOnChips -

Chips and Cheese

Chips and Cheese

@ChipsandCheese9 -

Chips & SaaS

Chips & SaaS

@ChipsSaas -

Fabricated Knowledge

Fabricated Knowledge

@_fabknowledge_ -

witeken

witeken

@witeken -

Charlie Demerjian

Charlie Demerjian

@CDemerjian -

High Yield

High Yield

@highyieldYT -

Sravan Kundojjala

Sravan Kundojjala

@SKundojjala -

William Keating

William Keating

@SemiconAlpha -

siliconmemes

siliconmemes

@realmemes6 -

Dylan Patel

Dylan Patel

@dylan522p -

Wen-Yee Lee 李玟儀

Wen-Yee Lee 李玟儀

@Wenyee_Lee

Something went wrong.

Something went wrong.